Sivabalaji Sivasankarapandian., International Journal of Engineering Research and Applications www.ijera.com ISSN: 2248-9622, Vol. 15, Issue 3, March 2025, pp 207-210

**RESEARCH ARTICLE**

**OPEN ACCESS**

# **Reconfigurable FPGAs for Avionics Systems**

### Sivabalaji Sivasankarapandian\*

(\*Email: ssivabalaji04@gmail.com)

### ABSTRACT

This paper explores the use of FPGAs in the Aerospace and Avionics. This paper ARINC, TTP protocol and VHDL language, highlighting their advantages over ASICs. This Paper outlines the categories of DAL and procedural steps of DO-254 Standards steps.

\_\_\_\_\_

Keywords – FPGA, ARINC, TTP, TDMA, CAN, DO-254, DAL

Date of Submission: 15-03-2025

Date of acceptance: 31-03-2025

### I. INTRODUCTION

In the world of Electronics, FPGAs (Field-Programmable Gate Array) are a type of integrated that be reprogrammed after circuit can manufacturing, allowing for flexible and adaptable hardware solutions. In the Aerospace/Space applications, these FPGAs are used the introduction of the paper should explain the nature of the problem, previous work, purpose, and the contribution of the paper. The contents of each section may be provided to understand easily about the paper.

### II. FIELD PROGRAMMABLE GATE ARRAYS

Reconfigurable hardware (FPGAs) provides a significant amount of logic resources suitable for accelerating compute-intensive applications. The programmability and reconfigurable features of FPGAs make it possible to evaluate a custom design faster than ASICs, and therefore they explore many more implementation alternatives. These features allow us to find the optimal model to solve a given problem with multiple tradeoffs, requiring several attempts.

FPGAs can provide better performances with significantly less power consumption, which is essential for mobile, embedded platforms. For instance, in terms of performance per power, an FPGA-based Avionics more efficient than a GPUbased one. Indeed, FPGAs can use binary precision that reduces hardware resources for a higher clock rate, while CPUs and GPUs cannot.

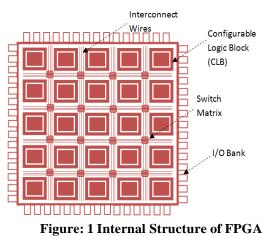

### **III. FPGA Internal Architecture**

The Configurable Logic Block(CLB) has 3 major implementation schemes, Look Up Table (LUT), MUX, Generic Array Logic [GAL]. Either method consists of programmable part which is used to realize logic part which holds value such as Flip Flop and selectors. I/O bank provides some control inputs pullup, pulldown, open drain, slew rate and etc. Avionics FPGAs primarily offer differential standard I/O banks because single standard I/Os are more vulnerable to radiation, electromagnetic field interference (EMI), and signal integrity issues. Switch Matrix (SM) are wiring channels between CLB to CLB or CLBs to I/O banks. Interconnect wires route the signals based on the Switch Matrix decisions.

Sivabalaji Sivasankarapandian., International Journal of Engineering Research and Applications www.ijera.com ISSN: 2248-9622, Vol. 15, Issue 3, March 2025, pp 207-210

### **IV. FPGAs in AEROSPACE and Avionics**

In aerospace and avionics, where safety and precision are critical, FPGAs provide unparalleled reliability, efficiency, and adaptability. They enable compliance with rigorous safety standards like DO-254 by supporting redundant, independent processing paths for safety-critical functions, such as real-time sensor data processing in avionics systems.

Optimized for power efficiency, FPGAs are ideal for compact, weight-sensitive applications. Their reconfigurable design powers adaptive flight control systems, allowing real-time updates and seamless integration of new requirements without hardware redesigns. With these capabilities, FPGAs enhance system reliability, reduce power consumption, and keep organizations at the forefront of aerospace innovation.

### V. ARINC protocols in FPGAs

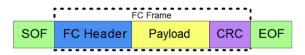

**ARINC:** Aeronautical Radio Incorporated (ARINC) is an aerospace standard that defines the characteristics of data transference inside aerospace avionic devices. ARINC 429 is a data transfer standard for aircraft avionics, utilizing a selfclocking and self-synchronizing data bus protocol with separate ports for transmission and reception. The physical connections use twisted pairs carrying balanced differential signaling. ARINC 818 is a packetized protocol focused on video applications, offering flexibility to support various complex video functions, such as multiplexing multiple video streams on a single link or transmitting a single stream over dual links. ARINC 708 is designed to transmit weather radar data, which enables the display of weather patterns on the aircraft's radar system. ARINC 623 is an ACARS messaging facilitates standard that direct datalink communication with air traffic control (ATC) for specific air traffic service (ATS) functions, including D-ATIS, ACARS-DCL (departure clearance outside the U.S.), and oceanic clearance. The ARINC 825 standard enhances the Controller Area Network (CAN) bus system for aviation and aerospace applications, providing advanced communication capabilities. ARINC 818 Avionics Digital Video Bus (ADVB) is a video interface and protocol standard developed for high bandwidth, low-latency, uncompressed digital video transmission in avionics systems.

FPGAs are frequently used to implement ARINC protocols like ARINC 429 and ARINC 818 due to their flexibility and ability to handle complex data processing and communication requirements in avionics systems.

| M  | SB |    |          |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |   |       |   |   |   |   |   | I | SB |

|----|----|----|----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|---|-------|---|---|---|---|---|---|----|

| 32 | 31 | 30 | 29       | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10  | 9 | 8     | 7 | 6 | 5 | 4 | 3 | 2 | 1  |

| P  | 55 | iM | MSB DATA |    |    |    |    |    |    |    |    | _  |    | LS |    |    |    |    |    |    | в  | SDI |   | LABEL |   |   |   |   |   |   |    |

### Figure: 2 ARINC429 Standard

### Figure: 3 ARINC818 Communication Standard

# VI. Time TRIGGERED PROTOCOL in FPGAs

In avionics, the Time-Triggered Protocol (TTP) is a deterministic communication protocol designed for real-time control systems. It is used in applications that require high reliability and predictability, including flight computers and engine controls. TTP ensures that messages are transmitted at scheduled times with minimal jitter, which is essential for real-time control systems. It uses a Time-Division Multiple Access (TDMA) method on replicated communication channels, enabling autonomous fault-tolerant message transport. TTP provides increased communication bandwidth compared to previous protocols such as ARINC 429, MIL-1553, and CAN. TTP is a masterless, multicast protocol, allowing any node to begin communication and send messages to multiple destinations simultaneously.

## VII. VHDL IN AVIONICS FPGAs

VHDL, a Hardware Description Language (HDL), is widely used in the design and verification of FPGA within aerospace and defense industries, supported by a large community and extensive tools.

Aerospace and avionics applications follow strict safety standards like DO-254. VHDL's detailed design capabilities ensure compliance, modeling and verifying complex digital circuits with high precision and reliability. In space, FPGAs need radiation-hardening, and VHDL enables robust designs to endure harsh conditions. VHDL is a strongly typed language. In essence, the data type of both the left-hand side (LHS) and the right-hand side (RHS) of a VHDL statement must match. Because of this strongly typed language advantage, the compiler and EDA tools help to find the errors in the functionality and reduces the unintended logic implementation in the end products.

### VIII. RECONFIGURABLITY AND RELIABLITY

FPGAs provide reconfigurability and reliability, enabling dynamic adaptation and fault tolerance through techniques like dynamic reconfiguration and spare resource use, ideal for flexible and robust applications.

FPGAs can be reconfigured during operation, adapting to new requirements or faults without shutdown. Parts can be reconfigured while others stay active, optimizing resources and minimizing disruption. This is useful in signal processing and fault-tolerant systems.

FPGAs can be designed with fault tolerance using techniques such as redundancy and spare resources to manage or recover from errors. reconfiguration Dynamic can replace faulty resources with spares, enhancing system reliability. SRAM-based FPGAs, which are often used, can be reconfigured in-circuit, making them useful for testing. prototyping and However, their configuration memory may be vulnerable to radiation effects. This reliability is essential in applications like aerospace, where systems that require high reliability and fault tolerance are critical. Some aerospace manufacturers enhance system reliability by using multiple FPGA vendors like Xilinx, Lattice, and Altera. If one FPGA malfunctions, it is identified and reconfigured while the other two provide correct outputs. This ensures reliability and reconfigurability in flight control systems, features present in FPGAs but not in ASICs. Multiple FPGAs balance redundancy to maintain safety.

### IX. DO-254 Stand ARD

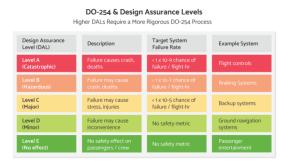

DO-254 is a rigorous standard designed to ensure the safety and reliability of airborne electronic hardware. It mandates a highly structured, repeatable, and requirements-based development process, accompanied by comprehensive documentation and verification activities. DO-254, or RTCA DO-254, is a design assurance guidance document for airborne electronic hardware, focusing on ensuring the safe and reliable operation of critical systems in aircraft. It covers the development, verification, and validation of electronic hardware, including Field-Programmable Application-Specific Gate Arrays (FPGAs), Integrated Circuits (ASICs), and other similar hardware components used in avionics systems. Design Assurance Levels (DALs): DO-254 defines five DALs (A to E) that determine the level of rigor required for the development and certification of the hardware, with DAL A being the most critical. DO-178C, which focuses on software development for airborne systems.

# Figure: 4 DO-254 Design Assurance level

### X. Disadvantages In FPGAs

Avionics systems require high reliability and safety standards, demanding rigorous testing that can extend development and increase costs. Aerospace applications must operate in highradiation environments, necessitating FPGAs designed to handle radiation effects. Single Event Effects (SEE), like single event upsets (SEUs) and single event transients (SETs), disrupt FPGA operations, requiring robust error detection and correction. Certification for aircraft use involves meeting strict safety and performance standards, which is a challenging process.

### **XI.** Conclusion

This Paper discussed the importance of reconfigurability and reliability in Avionics platforms and how FPGA are used to provide these features and how DAL standards are ensure the safety of the design in Aerospace applications. The Sivabalaji Sivasankarapandian., International Journal of Engineering Research and Applications www.ijera.com ISSN: 2248-9622, Vol. 15, Issue 3, March 2025, pp 207-210

Protocols available for Avionics FPGAs and the limitations were discussed

### REFERENCES

### **Journal Papers:**

- [1] Sasamal, T. N., & Prasad, R. (2011). Module based and difference based implementation of partial reconfiguration on FPGA: *A review. International Journal of Engineering Research and Applications (IJERA)*, 1(4), 1898-1903.

- [2] MohammedInthiyaz, S., B. Sumithra, and M. Tech. "FPGA Implementation of Radio Navigation Based on MicroBlaze." International Journal of Engineering Research and Applications (IJERA) Vol 3 (2013): 1032-1039.

- [3] Zemmouri, A., et al. "Integration and Implimentation System-On-A-Programmable-Chip (Sopc) In FPGA." *Journal of Theoretical and Applied Information Technology* 76.1 (2015): 127-133.

- [4] Mohammad, Imran, K. Ramananjaneyulu, and K. Veeraswamy. "FPGA implementation of a 64-bit RISC processor using VHDL." International Journal of Engineering Research and Applications (IJERA) 2.3 (2012): 2544-2549.

- [5] Mrabet, Hayder. *Design and Optimization of Reconfigurable Architectures: The FPGA Family*. Diss. Université Pierre et Marie Curie Paris VI, 2009.

- [6] Ayaz, Ibrahim, Ufuk Sakarya, and Ibrahim Hokelek. "Universal verification methodology-based airborne electronic hardware certification approach for ARINC-429." Aircraft Engineering and Aerospace Technology 95.7 (2023): 1145-1150.

#### **Books:**

[1] Bobda, Christophe, and Reiner Hartenstein. Introduction to reconfigurable computing: architectures, algorithms, and applications. Vol. 1, no. 1.5. Netherlands: Springer, 2007.