# RESEARCH ARTICLE

# **OPEN ACCESS**

# **6T SRAM Cell: Design And Analysis**

# Abhishek Agal\*, Pardeep\*, Bal Krishan\*\*

\* (Electronics Engineering Department, YMCA University of science & technology, Faridabad) \*\*(A.P., Electronics Engineering Department, YMCA University of science & technology, Faridabad)

# ABSTRACT

SRAM has become a major component in many VLSI Chips due to their large storage density and small access time. SRAM has become the topic of substantial research due to the rapid development for low power, low voltage memory design during recent years due to increase demand for notebooks, laptops, IC memory cards and hand held communication devices. SRAMs are widely used for mobile applications as both on chip and off-chip memories, because of their ease of use and low standby leakage.

The main objective of this paper is evaluating performance in terms of Power consumption, delay and SNM of existing 6T CMOS SRAM cell in 45nm and 180nm technology.

*Keywords* –6T SRAM cell, Power dissipation, Read Delay, SNM, Write Delay.

# I. INTRODUCTION

6T static random-access memory is a type of semiconductor memory that uses bistable latching circuitry to store each bit. The term static differentiates it from dynamic RAM which must be periodically refreshed. SRAM exhibits data remembrance, but is still volatile in conventional sense, that data is eventually lost when memory is not powered.

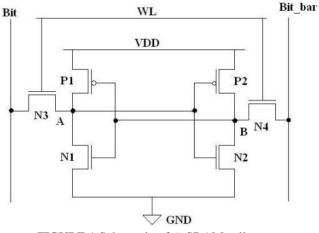

#### II. 6T SRAM CELL OPERATION 1. Standby Mode (the circuit is idle)

In standby mode word line is not asserted (word line=0), so pass transistors N3 and N4 which connect 6t cell from bit lines are turned off. It means that cell cannot be accessed. The two cross coupled inverters formed by N1-N2 will continue to feed back each other as long as they are connected to the supply, and data will hold in the latch.

#### 2. Read Mode (the data has been requested)

In read mode word line is asserted (word line=1), Word line enables both the access transistor which will connect cell from the bit lines. Now values stored in nodes (node a and b) are transferred to the bit lines. Assume that 1 is stored at node a so bit line bar will discharge through the driver transistor (N1) and the bit line will be pull up through the Load transistors (P1) toward VDD, a logical 1. Design of SRAM cell requires read stability (do not disturb data when reading).

#### **3.** Write Mode (updating the contents)

Assume that the cell is originally storing a 1 and we wish to write a 0. To do this, the bit line is lowered to 0V and bit bar is raised to VDD, and cell is selected by raising the word line to VDD.

Typically, each of the inverters is designed so that PMOS and NMOS are matched, thus inverter threshold is kept at VDD/2. If we wish to write 0 at node a, N3 operates in saturation. Initially, its source voltage is 1. Drain terminal of N2 is initially at 1 which is pulled down by N3 because access transistor N3 is stronger than N1. Now N2 turns on and P1 turns off, thus new value has been written which forces bit line lowered to 0V and bit bar to VDD. SRAM to operate in write mode must have writeability which is minimum bit line voltage required to flip the state of the cell.

FIGURE 1 Schematic of 6t SRAM cell

### III. PERFORMANCE PARAMETERS OF SRAM

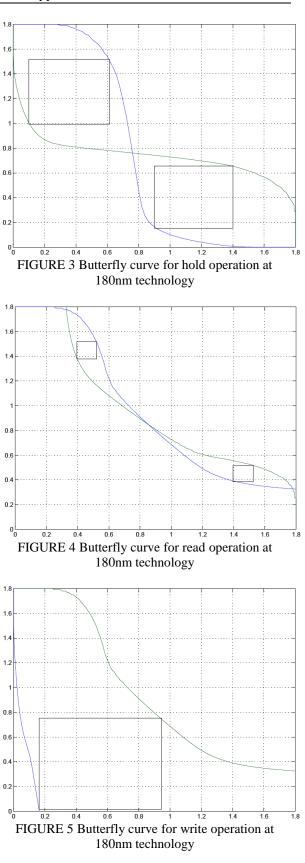

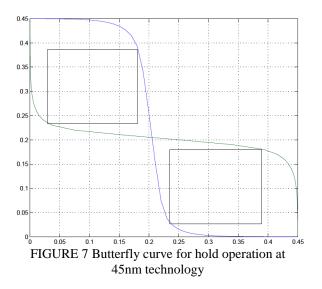

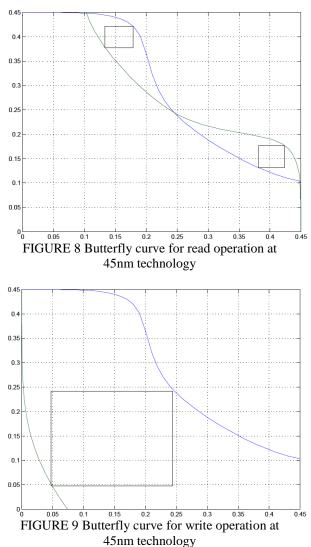

SNM: maximum dc voltage that the cell tolerates before it changes state in read mode. The size of the maximum square that can be inscribed in butterfly curve gives the SNM of the SRAM cell. Instead of measuring the read stability and write ability separately a method known as N-curve method by which both parameters can be arrived at simultaneously is used. Hold SNM is the maximum dc noise that the cell tolerates before it changes state in the hold mode.

Write delay: It is the delay between the applications of the word line WL signal and the time at which the data is actually written.

Read delay: Read delay is the delay involved in allowing the bit lines to discharge by about 10% of the peak value or the delay between the application of the WL signal and the response time of the sense amplifier.

**IV. RESULTS AND ANALYSIS**

FIGURE 2 Transient analysis at 180nm technology

- 1. Average power consumed = 1.317488e-004 watts.

- 2. Read delay = 4.7168e-010 sec.

- 3. Write delay= 9.6081e-010 sec.

- 4. Hold SNM=0.5 volt.

- 5. Read SNM=0.1 volt.

- 6. Write SNM=0.7 volt.

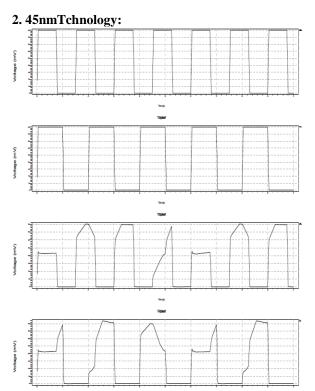

FIGURE 6 Transient analysis at 45nm technology

- 1. Average power consumed = 8.492199e-010 watts.

- 2. Read Delay = 4.7222e-010 sec.

- 3. Write Delay= 2.1395e-009 sec.

- 4. Hold SNM=0.15 volt.

- 5. Read SNM=0.05 volt.

- 6. Write SNM=0.2 volt.

## V. CONCLUSION

Simulation and analyzation of performance of 6T SRAM cells at 180nm and 45nm technology for parameters like power consumption, delay and SNM is as desired. Simulation results shows clearly how read, write operation is performed.

#### **VI.** ACKNOWLEDGEMENTS

For power constrained projects like space exploration and satellites the SRAM cell which consumes minimum power should be used while for very fast processing devices the SRAM cell which has minimum time delay should be used. The SRAM cell which has maximum SNM can be used in the device which works in noisy environment. The design of SRAM cell can be optimized by tradeoff between various performance parameters. New design is not introduced within the project. In future we will propose new SRAM cell design or schematic, which decreases read/write delay, consumes less power.

### REFERENCES

## **Journal Papers:**

- Ajay Kumar Dadoria, Arjun Singh Yadav, C.M Roy, "Comparative Analysis Of Variable N-T Sram Cells" International Journal of Advanced Research in Computer Science and Software Engineering, Volume 3, Issue 4, April 2013.

- [2] Seevinck, F. J. List, J. Lohstroh, "Static-Noise Margin Analysis of MOS SRAM Cells" IEEE J. Solid-State Circuits, vol. SC-22, pp. 748-754, Oct. 1987.

- [3] Sapna singh, Neha Arora, Meenkshi Suthar, Neha Gupta, "Performance evaluation of different SRAM cell structures at different technologies", International Journal of VLSI design& communication systems (VLSICS) vol.3, No.1, Februry 2012.

- [4] J. Rabaey, "Digital integrated circuits, A design perspective", prentice hall, upper saddle river, NJ, 1996.

- [5] Andrei Pavlov, Manoj Sachdev, "CMOS SRAM Circuit Design and parametric test in nano-scaled technologies, Process Aware SRAM Design and Test", springer, 2008.

- [6] M. Adiseshaiah, D. sharath Babu Rao, V. Venkateswara Reddy, "Implementation and Design of 6T SRAM with Read and write Assist circuits, IJREAS, Volume2, Issue 5 (May 2012), 2249-3905.

- [7] Ravindra kumar, Dr. Gurjit Kaur, "A Novel Approach to design of 6T (8X8) SRAM cell low power dissipation using MCML technique on 45NM", International Journal of Engineering Research and applications (IJERA), vol.2, Issue 4, July- August 2012, PP. 093-097

- [8] C.-T. Chuang, S. Mukhopadhyay, J.-J. Kim, K. Kim, R. Rao, "High-performance SRAM in nanoscale CMOS: Design challenges and techniques," in IEEE Int. Workshop., Memory Technology, Design and Testing, Taipei, Taiwan, Dec. 3-5, 2007, pp. 4-12.

- [9] H. Yamauchi, "A Discussion on SRAM Circuit Design Trend in Deeper Nanometer-Scale Technologies," IEEE Trans. Very Large Scale Integr. Syst. vol.18, no.5, pp.763-774, May 2010.

- [10] Arash Azizi-Mazreah, Mohammad T. Manzuri Shalmani, Hamid Barati and Ali Barati, "Delay and Energy consumption Analysis of conventional SRAM", World Academy of Science, Engineering and Technology no. 37, 2008.