## RESEARCH ARTICLE

**OPEN ACCESS**

# Design of Low Power Novel Viterbi Decoder Using Transmission Gates

# B. Vijayapriya, Dr.S. Padma, Prof.B.M. Prabhu,

PG scholar Angel college of engineering andtechnology, Tirupur Assistant Professor Angel college of engineering andtechnology, Tirupur Professor Sona College of Technology Salem

## Abstract

In this paper a low power viterbi decoder based on transmission gates is presented. In wireless communication, Viterbi decoder which consumes more power plays an important role in communication applications. Viterbi decoder is used to decode the received data which is encoded using convolutioncodes. In this paper in order to reduce the power consumption and to improve the performance of the decoder optimized transmission gate logic is proposed. As the multiplexer and flip flops are the major parts in the viterbi decodercircuit, transmission gate is used to reduce the complexity of the circuit. The proposed technique is simulated using tanner tool. The simulated result shows the power consumption of viterbi decoder using TG is lower compared to CMOS logic and also the number of transistors required to design the Viterbi decoder is reduced using TG logic.

Keywords: Viterbi decoder, transmissiongates, tanner tool

#### I. Introduction

Viterbidecoder is based on viterbialgorithmwhich was proposed by Viterbi in 1967. The algorithm is mainly used to decode the convolutioncodes in digital communication systems. Theviterbialgorithm(VA) provides the most accurate way to find maximum likelihood sequence of transmitted signal. In order to transmit the analog signal through the digital communication system, the signal should be sampled and quantized before proceeding through the system. In this paper, it is assumed that the digital values are transmitted through channel. The Viterbialgorithm is used to find the signals which are corrupted by noise in the channel.

Theviterbi decoder consists of three major blocks such as branch metric unit, add compare and select unit and survivor memory unit. The Viterbi algorithm is based on treills diagram and the encoder circuit is considered as a finite state machine. In order to find out the errors in the received sequence the hamming distance of that sequence is calculated. Viterbi decoders are widely used in wireless communication specifically it is widely used in third generation mobile terminals and the decoder circuit consumes more power in the transmission system

In presentscenario reducing the power consumed by a device is a major factor in VLSI technology. Even though the CMOS logic design plays a major role in designing devices with low power consumption, the switching activity of the CMOS devices causes more power consumption. For low power consumption, different logic styles may be used. In this paper, the design based on transmission

gate is proposed for low power consumption application.

## II. Proposed Design

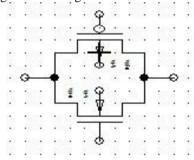

The proposed method is based on transmission gates. The transmission gate (TG) circuitis given in the figure 1.

Figure 1.A simple transmission gate

Transmission gate(TG) which consist of one n-MOSFET and one p-MOSFET acts as a switch where the NMOS passes strong '0' and the PMOS passes strong '1'. The transmission gate logic is often used for the design of multiplexers and Exclusive OR gates. Since the multiplexers and EXOR gates are the major blocks in many digital systems, the number of transistors and the power consumed is reduced by using TG logic.

## III. Design of viterbi decoder using TG

The Viterbi decoder consists of three major blocks such as Branch metric unit, Add compare and select unit and Survivor memory unit. In this chapter the blocks of viterbi decoder are explained using transmission gates.

www.ijera.com 972 | P a g e

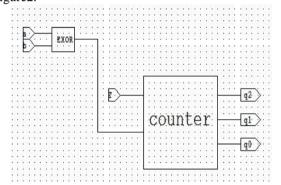

#### 3.1Branch Metric Unit

The Branch Metric Unit(BMU) is used to measure the Hamming Distance between the received sequences with the expected code sequence. The Hamming Distance is calculated simply by counting the number of bits at which the received sequence and the expected sequence are different. The BMU consists of a two input EXOR gate and three bit asynchronous counter. The counter is designed using T flipflops. The output of the EXOR gate is applied as the clock pulse to the first flip flop of the counter and output of one flipflop is given as clock input for the next flip flop. The T input for all flip flops are tied to HIGH input. When the received sequence and the expected sequence are different then the output of the EXOR gate becomes high and the counter starts to count. The circuit diagram for BMU is given in the figure2.

Figure 2.Block Diagram of BMU

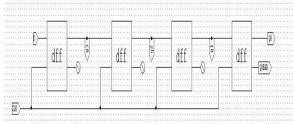

The counter is designed by cascading T flip-flopsand the T flip-flop is designed by using D flip-flop and gates. The circuit diagram for D flip-flop using TG is shown in figure 3.

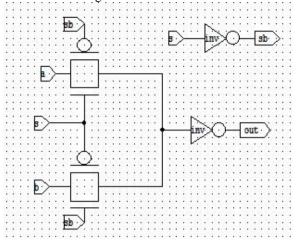

#### 3.2 Add Compare and Select Unit

The Add Compare and Select unit (ACSU) consists of adder, comparator and selector. The adder unit adds the branch metric from the BMU with the corresponding path metric. The inputs to the adder are the output of BMU and the previous path metrics. The new resultant metrics are compared in

Fig 3.Circuit diagram of D flipflop using TG

comparator. The multiplexer is the major block in the selector. The circuit diagram for multiplexer using TG is shown in figure4.

Fig 4.Circuit diagram for 2 to 1 multiplexer using TG

The selector selects theappropriate branch. The selector unit consists of four 2:1 multiplexers. Theoutputs of adder unit are given as inputs to the selector unit. The output (less than bit) of the comparator is given as selection line for the selector.

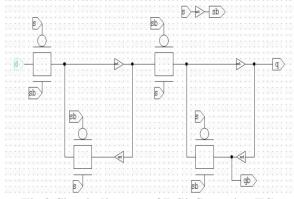

#### 3.3 Survivor memory unit

The important step in the decoding process is finding the survivor path. The output of the selector is the survivor path and that path is stored in the survivor memory unit. The survivor memory unit (SMU) is designed by cascading serial in serial out (SISO) shiftregisters. The length of the shift registers depends on the length of the encoder. The SMU unit consists of four SISO shift registers. When the positive clock pulse is applied, the data D is transferred to the output of the flip-flop and for each positive clock cycle the value stored in one register is shifted to another register.

Figure 5: Block diagram of single stage of SMU

#### 3.4 Block diagram of viterbi decoder

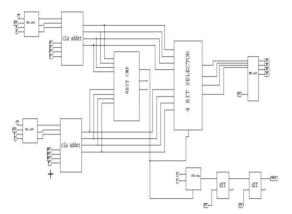

The block diagram of viterbi decoder with TG isshown in figure 6.The circuit is designed using Tanner tool. in this circuit two BMU units are used since there are two possible state changes from one state to another state. The BMU unit calculates the Branch metric. The ACSU adds the branch metric with the previous path metric using adder.

www.ijera.com 973 | P a g e

Fig 6.Block diagram of viterbi decoder

The comparator adds two paths from two adders and the selector selects the path with minimum hamming distance .The SMU stores the new path metric value and the corresponding states. The 2:1multiplexer and two bit shift registers are used to get the decoded output.

#### IV. Results and Discussion

The viterbi decoder designed Transmission logic gates are simulated using Tanner tool (TSPICE)in 20µm technology. The output waveform of the viterbi decoder is shown in the figure 7. When the select input is logic 1, then the 'a' input value is transferred to the output. In the BMU the clock signal for the counter is applied from the ouput of EXOR gate. There are two BMUs since each state has two branches in treills. The output of the EXOR gate is the Hamming distance between the expected sequence and the received sequence that can be counted by using the counter. The output of the BMU denotes the branch metric value. In ACSU the branch metric values are added with the Path metric value and the appropriate path is selected in selector unit using the control signal from the comparator unit. The Less than (LT) output of the comparator is used as a selection line of the selector unit and the multiplexor. When the select input is logic '0', then the 'b' input value is transferred to the output.

Fig7.Output waveform of Viterbi Decoder Using TG

## 4.1 Comparison of performance

The Viterbi decoder is designed using transmission gates in circuit level. The performance of viterbi decoder is analyzed using the simulated output in Tanner tool. The simulation results show that the power consumption,the no of transistors of the Viterbi decoder using TG are reduced compared to the existing CMOS logic.Hence the results prove that the proposed TG logic has low power, high speed and low area. The performance comparison table for Viterbi decoder with 5v vdd is given in Table1. The performance comparison table for Viterbi decoder with 3vvdd is given in Table2.The performance comparison table for Viterbi decoder with 1.5vvdd is given in Table3.

## V. Conclusion

The major blocks of Viterbi decoder are simulated by using Tanner's s-edit VLSI CAD tools and Parameters values are analyzed by using same tool. The circuits were compared with existing CMOS circuits. The circuit based on Transmission Gate gives better performance than existing circuits in term of power dissipation and Area. The proposed circuits can be used in the low power wireless communication.

TABLE.1. VITERBI DECODER WITH Vdd = 5.0Volts

| S.no | Viterbi<br>decoder | Power (mW) | Transistor count | Area μm <sup>2</sup> | Speed<br>(Ghz) | Delay<br>(ns) | PDP(10 <sup>-12</sup><br>W-s) |

|------|--------------------|------------|------------------|----------------------|----------------|---------------|-------------------------------|

| 1    | CMOS               | 0.058      | 982              | 0.043208             | 5.157          | 193.21        | 11.20                         |

| 2    | TG                 | 0.041      | 838              | 0.036872             | 13.33          | 74.98         | 3.074                         |

www.ijera.com 974 | P a g e

| S.no | Viterbi | Power | Transist | Area μm <sup>2</sup> | Speed | Delay | PDP(10 <sup>-12</sup> |

|------|---------|-------|----------|----------------------|-------|-------|-----------------------|

|      | decoder | (mW)  | or count |                      | (Ghz) | (ns)  | W-s)                  |

| 1    | CMOS    | 0.95  | 982      | 0.043208             | 6.456 | 154.6 | 146.87                |

| 2    | TG      | 0.71  | 838      | 0.036872             | 18.55 | 53.90 | 38.269                |

TABLE.2. VITERBI DECODER WITH Vdd = 3.0Volts

| TARIF 3 | VITERBI DECOD | FR WITH Vdd - | 1.5 Volte |

|---------|---------------|---------------|-----------|

|         |               |               |           |

| S.no | Viterbi | Power | Transist | Area μm <sup>2</sup> | Speed | Delay  | PDP(10 <sup>-12</sup> |

|------|---------|-------|----------|----------------------|-------|--------|-----------------------|

|      | decoder | (mW)  | or count |                      | (Ghz) | (ns)   | W-s)                  |

| 1    | CMOS    | 5.467 | 982      | 0.043208             | 9.22  | 108.45 | 592.45                |

| 2    | TG      | 3.291 | 838      | 0.036872             | 26.61 | 37.57  | 123.64                |

#### References

- Jinjin He, Huaping Liu, Zhongfeng Wang, [1] Xinming Huang, and Kai Zhang "High-Speed Low-Power Viterbi Decoder Design for TCM Decoders ", IEEE transactions on very large scale integration (vlsi) systems, VOL. 20, NO. 4. APRIL 2012.

- [2] V. Anish Kumar, T. Kalavathi devi and P.Sakthivel "An Efficient Low Power VLSI architecture for Viterbi Decoder using Null Convention Logic", International Conference on VLSI, Communication & Instrumentation 2011, proceedings published by International Journal of Computer Applications.

- Jie Jin and Chi-yingTsui" Low-Power [3] Limited-Search Parallel State Viterbi Decoder Implementation Based on Scarce State Transition" IEEE transactions on very large scale integration (vlsi) systems, VOL. 15, NO. 10, OCTOBER 2007

- Meilana Siswanto1, Masuri Othman, [4] Edmond Zahedi, 2006 "VLSI Implementation of 1/2 Viterbi Decoder for IEEE P802.15-3a UWB Communication", IEEE ICSE2006 Proc., Kuala Lumpur, Malaysia,666 - 670.

- Chien-Ching Lin, Yen-Hsu Shih, Hsie-[5] Chia Chang, and Chen-Yi Lee, 2005. "Design of a Power-Reduction Viterbi Decoder for WLAN Applications", IEEE Transactions on Circuits and System-I: regular papers, 52(6), 321-328G.

- Injin He, Zhongfeng Wang, Zhiqiang Cui, [6] and Li Li, 2009, "Towards an Optimal Trade-off of Viterbi Decoder Design", IEEE conferecne, 3030-3033

- [7] Dalia A., El-Dib and Elmasry M.I. 2004. "Modified Register-Exchange Viterbi Decoder for Low-Power Wireless Communications", IEEE Transactions on *Circuits and Systems I*, ,51(2), 371-378

- [8] Forney, 1973. "The Viterbi Algorithm", Proceedings of the IEEE, 61(3), 268-278.

- [9] Lang L, Tsui C.Y and Cheng R.S.1997. "Low power soft output Viterbi decoder scheme for turbo code decoding", IEEE Conference-Paper, ISCAS "97, New York, USA, 24, 1369-1372.

- [10] Jun Jin Kong, Keshhab K Parthi, 2004 "Low latency Architectures for High Throughput Rate Viterbi Decoder", IEEE Transactions on VLSI System, 12(6), 642-651

- [11] Irfan abib, Ozgun Paker, and Sergei Sawitzki,"Design Space Exploration of Hard-Decision Viterbi Decoding",2009.

# **AUTHOR DETAILS**

B. Vijayapriya. B.E, (M.E) received herB.E., degree in Electronics and Engineering communication from Coimbatore Institute of Engineering and

Technolgy (2011) Coimbatore. She is pursuing M.E Embedded Systems PG scholar in Angel College of Engineering and Technology, Tirupur and her area of Interest are Embedded Systems, Microcontroller and Processors, VLSI.

Prof. B. M. Prabhu, M.E., (Ph. D)., received his B.E., Electrical and Electronic Engineering from Anna University Chennai and M.E., VLSI

Design from Anna University Coimbatore. He is currently Ph.D in the field of Low Power VLSI. He has published 12 paper national conferences, 2 in international conferences and 2 international journals.

## Dr. S. Padma, M.E., Ph. D, Professor,

Department of Electrical and Electronics EngineeringSona College of Technology, Salem she received her B.E., Electrical and Electronics Engineering from Govt. College of Engineering, Salem-11 and M.E., Power Systems Engineering

www.ijera.com 975 | Page

www.ijera.com

from Annamalai University and Ph.D Flexible AC Transmission Systems from Anna University, Chennai, and 19 years of teaching experience then she has 5 Memberships in Professional bodies, she have published 11 International Journals, 11 National conferences and 3 International conference and she has published 6 books.

www.ijera.com 976 | P a g e