# A.Thejasree, A.Hemasekhar / International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 2, Issue 3, May-Jun 2012, pp.2655-2659 POWER FACTOR CORRECTION BY USING AC/DC CONVERTER WITH QUASI-ACTIVE SCHEME

## A.Thejasree\*

P.G.Student [PE&ED] Dept.of EEE S.V.P.C.E.T, Puttur A.Hemasekhar\*\*

Associate Professor Dept.of EEE S.V.P.C.E.T, Puttur

Abstract—This letter presents a novel ac/dc converter based on a quasi-active power factor correction (PFC) scheme. In the proposed circuit, the power factor is improved by using an auxiliary winding coupled to the transformer of a cascade dc/dc fly back converter. The auxiliary winding is placed between the input rectifier and the low-frequency filter capacitor to serve as a magnetic switch to drive an input inductor. Since the dc/dc converter is operated at highswitching frequency, the auxiliary windings produce a high frequency pulsating source such that the input current conduction angle is significantly lengthened and the input current harmonics is reduced. It eliminates the use of active switch and control circuit for PFC, which results in lower cost and higher efficiency. In order to achieve low harmonic content, the input inductor is designed to operate in discontinuous current mode. Operating principles, analysis, and experimental results of the proposed method are presented.

Index Terms —AC/DC converter, power factor correction, single stage.

### I. NTRODUCTION

#### CONVENTIONAL offline power converters with

distorted input current waveforms with high harmonic contents. To solve these problems, so as to comply with the harmonic standards such as IEC 61000-3-2, several techniques have been proposed to shape the input current waveform of the power converter. A common approach to improving the power factor is a two-stage power conversion approach. The two-stage scheme results in high power factor and fast response output voltage by using two independent controllers and optimized power stages. The main drawbacks of this scheme are its relatively higher cost and larger size and particularly in low power applications. In order to reduce the cost, the single-stage approach, which integrates the PFC stage with a dc/dc converter into one stage, is developed [1]–[11]. These integrated single-stage power factor correction (PFC) converters usually use a boost converter to achieve PFC with discontinuous current mode (DCM) operation.

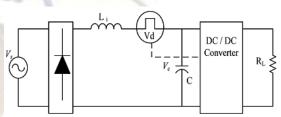

Fig1.General circuit diagram of dither rectifier with PFC cell. operation gives a lower total harmonic distortion (THD) of the input current compared to the continuous current mode (CCM). However, the CCM operation yields s lightly higher efficiency compared to the DCM operation.

Generally, single-stage PFC converters meet the regulatory requirements regarding the input current harmonics, but they do not improve the power factor and reduce the THD as much as their conventional two-stage counterpart. The power factor could be as low as 0.8, however, they still meet the regulation. The single-stage scheme is especially attractive in low cost and low power applications due to its simplified power stage and control circuit [5], [6]. To overcome the disadvantages of the single-stage scheme, many converters with input current shaping have been presented [3]-[12]. Another technique based on parallel connection of this dither signal is presented in [13], however, the harmonic content can meet the regulatory standard by a small margin. A new concept of quasi-active PFC is proposed to improve the efficiency of a single-stage converter by preventing the input current or voltage stress due the PFC cell from being added to the active switch. In this circuit, the dc/dc cell operates in DCM so that a series of discontinuous pulses is used to shape the input inductor current and the PFC is achieved.

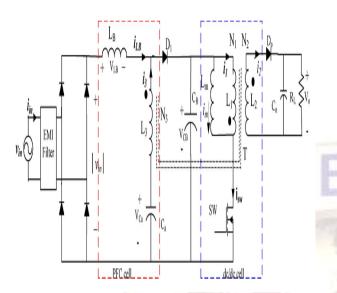

In this letter, a new technique of quasi-active PFC is proposed. As shown in Fig. 2, the PFC cell is formed by connecting the energy buffer (LB) and the transformer of the dc/dc cell, between the input rectifier and the lowfrequency filter capacitor used in conventional power converter. an auxiliary winding (L3)coupled t the transformer of the dc/dc cell, between the input rectifier and the lowfrequency filter capacitor used in conventional power converter.

Fig. 2. Proposed quasi-active PFC circuit diagram. Since the dc/dc cell is operated at high frequency, the auxiliary winding produces a high frequency pulsating source such that the input current conduction angle is significantly lengthened and the input current harmonics is reduced. The input inductor LB operates in DCM such that a lower THD of the input current can be achieved. Design example and the experimental results are presented in Section III.

II. PROPOSED QUASI-ACTIVE PFC CIRCUIT

The proposed quasi-active PFC circuit is analyzed in this section. As shown in Fig. 2, the circuit comprised of a bridge rectifier, a boost inductor LB, a bulk capacitor Ca in series with the auxiliary windings L3, an intermediate dc-bus voltage capacitor CB, and a discontinuous input current power load, such as fly-back converter. The fly back transformer (T) has three windings N1,N2, and N3. The secondary winding N2 =1 is assumed. In the proposed PFC scheme, the dc/dc converter section offers a driving power with high-frequency pulsating source. The quasi-active PFC cell can be considered one power stage but without an active switch.

To simplify the analysis, the following assumptions have been made.

All semiconductors components are ideal. 2)The power transformer does not have the leakage inductances because of the ideal coupling.

All the capacitors are high enough so that the voltage across them is considered constant.

Finally, the input voltage of the converter is considered constant during as switching cycle because the switching frequency is much higher than the line frequency.

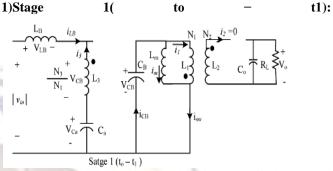

**A.** Principles of Operation of the Proposed Circuit To facilitate the analysis of operation of stages and the key waveforms of the proposed circuit. It is assumed that both the input inductor LB and the magnetizing inductance of the fly back converter operate in DCM. Therefore, currents iLB ,im , and i2 are zero at the beginning of each switching period. It is also assumed that the average capacitor voltage VCa is greater than the average rectified input voltage |vin|. To ensure proper operation of the converter, the transformer's turns ratio should be (N1 /N3)  $\geq$  2 and the boost inductor LB <Lm .In steady-state operation, the topology can be divided into four operating stages.

When the s witch (SW) is turned on at t = to, diodes D1 and Do are OFF, therefore, the dc-bus voltage VCB is applied to the magnetizing inductor Lm, which causes the magnetizing current to linearly increases. This current can be expressed as

$$i_m = \frac{V_{CB}}{L_m}(t_o - t_1).$$

(1)

since diode D1 is OFF, the input inductor LB is charged by input voltage, therefore, the inductor current iLB is linearly increased from zero since it is assumed that the PFC cell operates in DCM. This current can be expressed as

$$i_{LB} = \frac{|V_{\rm in}| + (N_3/N_1)V_{CB} - V_{Ca}}{L_B}(t_o - t_1)$$

(2) where

Vin = Vm | sin  $\theta$ | is the rectified input voltage,(to - t1) = dTS is the ON-time of t he switch (SW), LB is the boost inductor and N1, N3 are t he primary and auxiliary turns ratio, respectively. At this stage, iLB = -i3 and the capacitor Ca is in the charging mode. On the other hand, Do is reversed biased and there is no current flow through the secondary winding.

$$i_1 = \frac{N_3}{N_1}i_{LB} = -\frac{N_3}{N_1}i_3.$$

(3)

Thus

$$i_m = i_{CB} - i_1 = i_{CB} + \frac{N_3}{N_1}i_3.$$

(4)

Therefore, it can be seen that the magnetizing current im is supplied by the discharging current from the dc bus capacitor CB and the current i3 which is equal to input current iLB at this stage. The current through the main switch (SW) is given by

$$i_{\rm SW} = i_{CB} = i_m - \frac{N_3}{N_1}i_3 = i_m + \frac{N_3}{N_1}i_{LB}.$$

(5)

Therefore, the current stress of the switch can be reduced by selecting the turns ratio (N3 /N1), which is designed to be less than 1 to ensure proper operation of the transformer. Compared to the single-stage BIFRED converter [11], the switch current is given by

And

$$i_{SW} = i_m + i_{LB}$$

. (6)

Obviously, the proposed circuit has less switch current stress therefore, the conduction loss and switching losses are reduced and the efficiency is improved correspondingly.

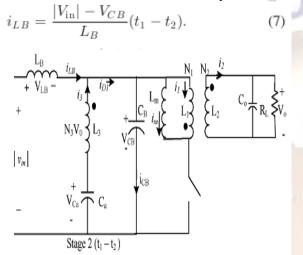

2) Stage 2 (t1 - t2): When the switch is turned OFF at t=t1, output diode Do begins to be forward biased. Therefore, the energy stored in the transformer magnetizing inductor is delivered to the load through the secondary. Similarly, the diode D1 is also forward biased and the voltage across LB now Vin–VCB. Therefore, the current ILB is linearly decreased to zero at t = t2 (DCM operation), and the energy stored in LB is delivered to the dc bus capacitor CB.

The capacitor (Ca) is also discharging its energy to the dc bus capacitor CB and the current i3 reverse its direction. Therefore, the capacitor current is given by

$$i_{D_1} = i_{CB} = i_{LB} + i_3.$$

(8)

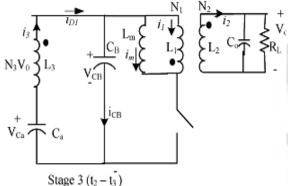

3) Stage 3 ( $t_2 - t_3$ ): At this stage, the input inductor current iLB reaches zero and the capacitor

Ca continues to discharge its energy to the dc bus capacitor CB. Therefore, iD1 = iCB = i3. At t= t3, the magnetizing inductor releases all its energy to the load and the currents im and i2 reach to zero level because a DCM operation is assumed.

4) Stage 4 (t3 - t4): This stage starts when the currents im and i2 reach to zero. Diode D1 still forward biased, therefore, the capacitor Ca still releasing its energy to the dc bus capacitor CB.

Stage 4 (t<sub>3</sub> – t<sub>4</sub>)

This stage ends when the capacitor Ca is completely discharged and current i3 reaches zero. At t = t5, the switch is turned on again to repeat the switching cycle.

**B. Steady-State Analysis**

The voltage conversion ratio of the proposed converter can be estimated from the volt-second balance on the inductors and the input–output power balance as explained in the following.

$$\left(V_{\rm in} + \frac{N_3}{N_1} V_{CB} - V_{Ca}\right) dT_S = \left(V_{CB} - V_{\rm in}\right) d_1 T_S \qquad (9)$$

where

d1 is the OFF-time of the switch (SW). Therefore, d1 could be given by

$$d_1 = \frac{V_{\rm in} + (N_3/N_1) V_{CB} - V_{Ca}}{V_{CB} - V_{\rm in}} d.$$

(10)

From

Fig. 3(a), the average current of the boost inductor in a switching cycle is given by

$$I_{\rm in} = I_{LB,\rm av} = \frac{i_{LB,\rm peak}}{2} \left(d + d_1\right) T_S.$$

(11)

Substituting for iLB, peak given (12) and using(10),the average input current is given by

$$I_{\rm in} = \frac{V_{\rm in} + (N_3/N_1) V_{CB} - V_{Ca}}{2L_B} d^2 T_S \\ \times \left(\frac{(1+N_3/N_1) V_{CB} - V_{Ca}}{V_{CB} - V_{\rm in}}\right).$$

(12)

Based

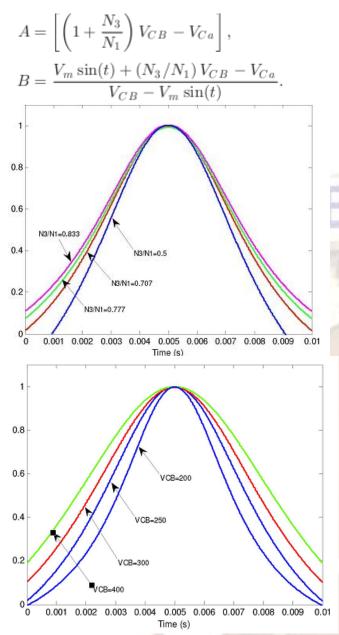

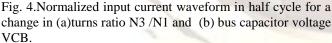

on (12) for a given input voltage, Fig. 4(a) shows the normalized input current waveform in a half cycle for a change in the turns ratio N3 /N1. It can be seen that to reduce the dead time and improve the power factor of the input current the turns ratio must be  $\geq 0.5$ . Similarly, Fig. 4(b) shows the normalized input current waveform for a change in dc bus capacitor voltage VCB.The energy absorbed by the circuit from the source during a half switching cycle is given by

$$P_{\rm in} = \frac{1}{\pi} \int_0^\pi V_m \sin(t) I_{\rm in} dt.$$

Substitution for Iin in given (12) yields

$$P_{\rm in} = \frac{1}{\pi} \frac{V_m}{2L_B} d^2 T_S(A) \int_0^{\pi} \sin(t) B dt$$

(13)

Where

The average output power for a DCM fly back converter is given by

$$P_o = \frac{V_{CB}^2}{2L_m} d^2 T_S \,.$$

Assume 100% efficiency, Pin = Po , yields

(14)

$$V_{CB}^{2} = \frac{V_{m}}{\pi} \frac{L_{m}}{L_{B}} (A) \int_{0}^{\pi} \sin(t) B dt.$$

(15)

Equation (15) shows that the dc bus capacitor is independent of load variation.

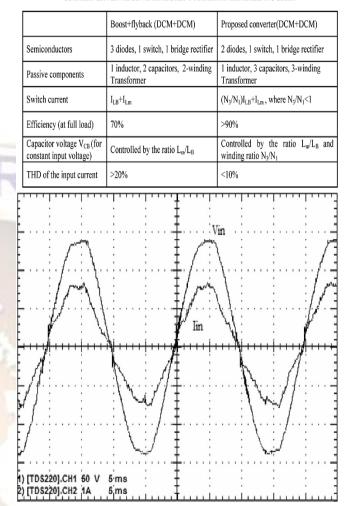

Fig. 5. Measured input voltage and filtered input current at full load (THD = 8.2%).

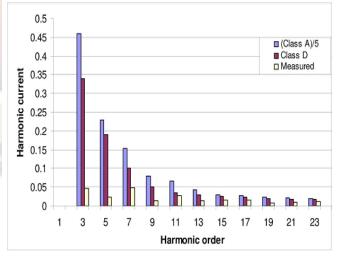

Fig. 6. Measured harmonics content of the input current.

#### **IV. CONCLUSION**

In this, a new ac/dc converter based on a quasi-active PFC scheme has been presented. The proposed method produces a

current with low harmonic content to meet the standard specifications as well as high efficiency. The input inductor can operates in DCM to achieve lower THD and high power factor. By properly designing the converter components, a tradeoff between efficiency and harmonic content can be established. Operating principles, analysis, and simulation results of the proposed method are presented.

### REFERENCES

- O. Gracia, J. A. Cobos, R . Prieto, and J. Uceda, "Single-phase power factor correction: A survey," IEEE Trans. Power Electron., vol. 18, no. 3,pp. 749– 755,May-2003.

- [2] R. R edle, L. Balogh, and N. O. Sokal, "A new family of single-stage isolated power factor correctors with fast regulation of the output vo ltage,"in Proc. IEEE PESC 1994 Conf., pp. 1137–1144.

- [3] C. Qian and K. Smedley, "A topology survey of single-stage p ower factor with a boost type inputcurrent-shaper," IEEE Trans. Power Electron., vo l. 16, no. 3, pp. 360–368, May 2001.

- [4] T.-F. Wu ,T.-H.Yu , and Y.C.Liu, "An alternative approach to synthesizing single-stage converters with power factor correction feature," IEEE Trans. Ind. Electron., vol. 46, no. 4, pp. 734–748, Aug.1999.

- [5] L. Huber, J. Zhang, M. Jovanovic, and F.C. Lee, "Generalized topologies of single-stage input-currentshaping circuits," IEEE Trans. PowerElectron., vol. 16, no. 4, pp. 508–513, Jul. 2001.