## An Improved Mesh Network for Massively Parallel Computers

N. Gopalakrishna Kini\*, M. Sathish Kumar\*\*

\* (Dept of Computer Science and Engineering, Manipal Institute of Technology, Manipal University, Manipal, India <u>ng.kini@manipal.edu</u>)

\*\* (Dept. of Electronics and Communication, Manipal Institute of Technology, Manipal University, Manipal, India <u>mskuin@yahoo.com</u>)

#### ABSTRACT

Mesh is one of the well-known interconnection networks among the parallel architectures in massively parallel computers. Simple and efficient parallel algorithm has been devised for efficient execution on it. We propose a new class of parallel architectures that can reduce the cost of the network without affecting the complete connectivity of the existing network. Accordingly existing parallel algorithm can be extended to this proposed new architecture.

*Keywords*- Parallel architectures, interconnection networks, parallel algorithms, mesh network.

### I. INTRODUCTION

Parallel processing is an efficient form of information processing which emphasize the exploitation of concurrent events in the computing process. In order to achieve significant performance in parallel computing, it is necessary to keep the communication overhead as low as possible. In parallel computers, interconnection networks are exploited to realize the required communication between processors. There is a need to fill the communication speed gap between processors [1].

To achieve parallel processing, it is required to develop more capable computer systems. Every interconnection network which connects the different subsystems in a machine is running into several limitations. High node degree will have impact on topological as well as economical cost of the network and network with high latencies will have a direct impact on the system performance [2][3]. On the other hand, in some networks the node degree increases proportionately as the network is scaled up which leads to modify the design of the network from the scratch [4].

The interconnection network is an important component in a parallel computer. A good interconnection network is expected to have least number of links, topological network cost and more reliable [4]. The interconnection network must be able to scale up with a few building blocks and with minimum redesign.

Massively parallel computing systems are placing a major emphasis on scalable networks with small diameters and bounded node degree. Mesh is a network with constant node degree and has a highly scalable architecture but has larger network diameter [4] [5] [7].

Node degree and network diameter are considered as the major concern in this work. In this paper, a new topology superimposed on the existing mesh network is proposed. This improved mesh network will have smaller node degree and better network diameter compared to existing mesh network.

# II. MESH INTERCONNECTION NETWORK

A 2-D mesh network can have l rows and m columns, in which an internal node is connected to nodes directly north, south, east and west of it [1][2][3][4]. In two-dimensional mesh network, N processors ( $\sqrt{N} \times \sqrt{N}$ ) are connected in 2-D topology.

A two-dimensional mesh network allows its nearest-neighbor processors to communicate

each other. This network is found to be relatively cheap as the scalability does not affect the node degree. Each processor address is identified with its row number *i* and column number *j* and will be interpreted with its address as (i, j). Communication can be provided connecting the processors for all  $0 \le i, j < \sqrt{N}$ .

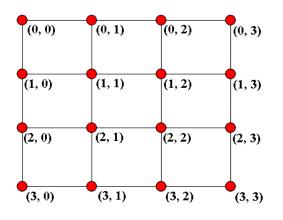

Fig. 1 A  $4 \times 4$  mesh network

Fig. 1 shows a  $4 \times 4$  mesh network connecting 16 processors [5][6]. A processor can be addressed with its row number and column number and hence the network provides the connectivity among the nodes based on equations (1), (2), (3) and (4).

The data routing functions of mesh interconnection network is

| $R_{+row}(i, j) = ((i+1), j)$ | for $0 \le i < \sqrt{N}$ -1 and $0 \le j < \sqrt{N}$                             |

|-------------------------------|----------------------------------------------------------------------------------|

| <b>D</b> (; ) ((; 1) )        | (1)<br>for $0 < i \le \sqrt{N}$ -1 and $0 \le j < \sqrt{N}$                      |

| $K_{-row}(l, j) = ((l-1), j)$ | $ \text{for } 0 < i \leq \sqrt{N} - 1 \text{ and } 0 \leq j < \sqrt{N} $ $ (2) $ |

| $R_{+col}(i, j) = (i, (j+1))$ | for $0 \le i < \sqrt{N}$ and $0 \le j < \sqrt{N}$ -1                             |

|                               | (3)                                                                              |

| $R_{-col}(i, j) = (i, (j-1))$ | for $0 \le i < \sqrt{N}$ and $0 < j \le \sqrt{N}$ -1                             |

|                               | (4)                                                                              |

The design procedure is fine-tuned and network is analyzed through multiple communication benchmarks that measure the node degree, network diameter, total number of links offered by the network and topological network cost involved.

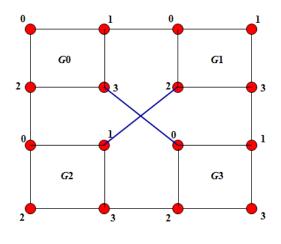

A 4 × 4 modified mesh network is shown in fig. 2. In obtaining this network, designer will have to view the network in a slight different way. *N* processors are grouped equally into  $\sqrt{N}$  processor nodes. Such grouping is identified as group *G*0, G1, G2, and G3 as shown in Fig. 2. Now the designer will have so many independent mesh networks.

Here each group is with a 2-D mesh topology in which a processor is connected to processors that falls to the east, west, north and south of it. These independent networks are now connected with additional links (blue in color in Fig.2) to form a complete network. Certain protocols will have to be followed in formation of the group and providing the additional links among the groups of the network of different sizes.

By connecting such 2-D meshes using additional links we can reduce the number of links in modified mesh network. It is self-explanatory in Fig. 2 when compared with Fig. 1. Each processor address is identified with group number and processor number and will be interpreted with its address as *xy* coordinates. Communication can be provided connecting the any of the processors in the network.

**Fig. 2** A  $4 \times 4$  modified mesh network

### III. RESULT

The result in TABLE 1 show that for simple mesh network the node degree is 4 and that of improved mesh is 3.

TABLE 1 Node degree analysis

| No. of processors<br>Network type | 16 | 32 | <mark>6</mark> 4 | 256 | 1024 | 4096 |

|-----------------------------------|----|----|------------------|-----|------|------|

| Simple Mesh                       | 4  | 4  | 4                | 4   | 4    | 4    |

| Improved Mesh                     | 3  | 3  | 3                | 3   | 3    | 3    |

In improved mesh network the node degree also remains constant like in simple mesh irrespective of scalability of the system. Hence the topological cost per node is reduced by a link and hence reduction in the cost of the network without affecting the complete connectivity of the existing network.

### **IV. CONCLUSION**

We have analyzed an improved mesh interconnection network and compared it with simple mesh network. Mesh is a popular interconnection network used in parallel architectures for massively parallel computers. It has gained such popularity due to its constant node degree and has a highly scalable architecture. We have proposed a new class of parallel architecture that can reduce the cost of the network without affecting the complete connectivity of the existing network. This improved mesh network exhibits all the features of the simple mesh network and can be a best candidate in place of simple mesh network.

### REFERENCES

[1] K. Hwang, "Advanced Computer Architecture: Parallelism, Scalability, Programmability," New York McGraw-Hill, 1993.

[2] Hesham El-Rewini and Mostafa Abd-El-Barr, "Advanced Computer Architecture and Parallel Processing," John Wiley & Sons, Inc., Hoboken, New Jersey, 2005.

[3] J. L. Hennessy and D. A. Patterson, "Computer Architecture: A Quantitative approach,"  $3^{rd}$  ed., Morgan Kaufmann, 2005.

[4] N. Gopalakrishna Kini, M. Sathish Kumar and Mruthyunjaya H. S., "Analysis and Comparison of Torus Embedded Hypercube Scalable Interconnection Network for Parallel Architecture," *International journal of Computer Science and Network Security*, vol. 9, No.1, pp: 242-247, Jan. 2009.

[5] N. Gopalakrishna Kini, M. Sathish Kumar, Mruthyunjaya H.S., "An Efficient Routing Algorithm for an Injured Mesh Embedded Hypercube Interconnection Network" *International Conference on Electronic Design and Signal Processing, ICEDSP – 2009*, Manipal Institute of Technology, Manipal, India, Dec 10-12, 2009.

[6] Francis Zane, P.Marchand, R.Paturi and S. Esener, "Scalable network architecture using OTIS," *Journal of Parallel and Distributed Computing*, 2000, pp. 521-538.

[7] N. Gopalakrishna Kini, M. Sathish Kumar, Mruthyunjaya H.S., "A Torus Embedded Hypercube Scalable Interconnection Network for Parallel Architecture," *IEEE International Advance Computing Conference (IACC'09)*, Patiala, India, pp.2087-2090, Mar 6-7, 2009.